Introduction:

In the realm of computer architecture, performance evaluation is paramount for optimizing system efficiency and throughput. One crucial metric used to gauge the efficiency of a processor is CPI, or Cycles Per Instruction. This article aims to elucidate the concept of CPI, its importance in computer architecture, and its implications for system design and performance enhancement.

I. Unveiling CPI:

Deciphering Cycles Per Instruction A. Definition and Fundamental Concept B. The Relationship Between CPI, Clock Cycles, and Instructions Executed C. CPI as a Measure of Processor Efficiency and Performance

II. The Role of CPI in Assessing Processor Performance A.

Evaluating Instruction-Level Parallelism (ILP) B. Understanding Pipeline Efficiency and Stall Cycles C. CPI Variations Across Different Instruction Types and Architectures

III. Factors Influencing CPI A.

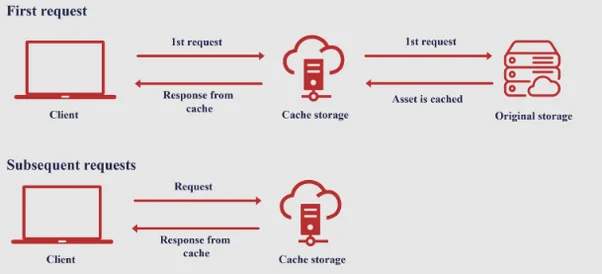

Instruction Set Architecture (ISA) Design B. Memory Hierarchy and Cache Performance C. Pipelining and Superscalar Execution

IV. CPI Calculation and Analysis A.

Methodologies for Measuring CPI B. Case Studies and Real-World Examples C. Interpreting CPI Data and Identifying Bottlenecks

V. Strategies for Reducing CPI and Improving Processor Efficiency A.

Instruction-Level Parallelism (ILP) Techniques B. Cache Optimization and Memory Access Optimization C. Pipeline Enhancements and Branch Prediction Algorithms

VI. Trade-offs and Considerations in CPI Optimization A.

Balancing CPI Reduction with Energy Consumption B. Architectural Design Trade-offs: Performance vs. Complexity C. Long-Term Implications of CPI Optimization Strategies

VII. CPI in Modern Processor Architectures A.

Evolution of CPI Metrics Across Generations B. Impact of Multi-Core Processors on CPI Evaluation C. Emerging Trends in CPI Optimization and Performance Enhancement

VIII. Practical Applications and Real-World Significance of CPI A.

High-Performance Computing (HPC) and Scientific Applications B. Embedded Systems and IoT Devices C. Cloud Computing and Data Center Infrastructure

Conclusion:

CPI, or Cycles Per Instruction, serves as a critical metric for assessing processor efficiency and performance in computer architecture. By understanding the factors influencing CPI and employing optimization strategies, architects and designers can enhance system throughput, reduce latency, and improve overall efficiency. As technology continues to evolve, the importance of CPI optimization remains paramount for driving innovation and pushing the boundaries of computational capabilities.